# CORNERSTONE DESIGN GUIDELINES 220 nm SOI Passive MPW #45 April 2025

# SIGN-UP DEADLINE: 30/05/2025 MASK SUBMISSION DEADLINES: 11/06/2025 (SOFT) AND 25/06/2025 (HARD) All deadlines end at 1PM (13:00) GMT

# **1. TERMS AND CONDITIONS AND COST**

All design submissions must agree with the terms and conditions:

www.cornerstone.sotonfab.co.uk/terms-and-conditions

Under no circumstances will we accept designs without agreement with the terms.

Therefore, we strongly recommend that the terms and conditions are pre-authorised by your institution prior to the mask submission date.

A purchase order (PO) must be uploaded at the same time as submitting your mask design in order pay the access fee, detailed in Table 1 below. Purchase orders will not be accepted via email.

| Design Area [mm²]                                                    | 11.47 x 4.9 | 5.5 x 4.9 | Delivery Time |  |

|----------------------------------------------------------------------|-------------|-----------|---------------|--|

| Access Cost with Heaters*                                            | £14,250     | £10,500   | 14 weeks      |  |

| Access Cost without Heaters*                                         | £ 9,000     | £ 6,250   | As above      |  |

| Access cost for Enterprises and<br>Academia based in UK <sup>†</sup> | 50% off     | 50% off   | As above      |  |

## Table 1 – Access cost and Delivery Time.

\*Quoted prices are exclusive of VAT, import duties/customs fees, withholding taxes etc.

#### <sup>†</sup>Are you a UK company or academic?

UK companies and universities may be eligible for a 50% discount on the cost of this MPW run with support from the CORNERSTONE Photonics Innovation Centre (C-PIC) (EP/Z531066/1), funded by UK Research and Innovation. Support will be provided under the Subsidy Control Act (2022) via Minimal Financial Assistance. To be eligible you will need to demonstrate the potential impact of receiving assistance against one or more of the following categories: impact on jobs and skills, access to new technology, accelerating product development. Following submission of your sign-up form, you will receive correspondence with more details of how this support will be provided. The support is only available to UK companies using CORNERSTONE for prototyping and product development.

To receive Design Rule Check (DRC) feedback from the CORNERSTONE team, users must submit their designs no later than the soft deadline. A two-week DRC window for resubmissions will then be available to those who submit their designs before the soft deadline. Submissions received after the soft deadline will not be checked against design rules; therefore, any fabrication failures related to design rule violations will be at the users' own risk. Submissions received after the hard deadline will not be accepted under any circumstances.

For information about setting up CORNERSTONE as a supplier to your institution, please contact <u>cornerstone@soton.ac.uk</u>.

## 2. DESIGN RULE AND COMPONENT CHANGES FROM PREVIOUS CALL (MPW #41)

• Mach-Zehnder interferometer (MZI) added to Components Library

## 3. IPKISS PROCESS DESIGN KIT

For the greatest functionality, we recommend that you use Luceda's IPKISS software to access the process design kit (PDK), after purchasing the required license. The IPKISS platform enables the automation and integration of all aspects of your photonic design flow in one tool, using one standard language. The PDK can be used in either IPKISS' Python coding environment or in the GUI of Siemens EDA L-Edit by using the IPKISS Link for Siemens EDA.

To obtain a copy of the software and a license key, please contact Luceda by sending an email to <u>info@lucedaphotonics.com</u>, specifying that you require a license for CORNERSTONE PDK usage. Luceda will contact you within 1-2 working days following the receipt of your request to provide a quote for the license. Of course, if you already have a valid license, the PDK can be accessed free of charge.

For more information, please visit <u>www.lucedaphotonics.com</u>.

Once you have access to the Luceda software, in order to obtain a copy of the CORNERSTONE PDK, please contact Luceda support at <u>info@lucedaphotonics.com</u>. An account will be created for you at support.lucedaphotonics.com for any technical support on Luceda's IPKISS software or the CORNERSTONE PDK implementation.

We also have a PDK available for download in .gdsll format.

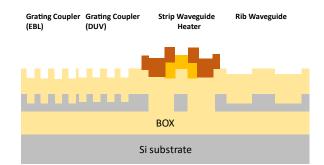

## 4. PROCESS FLOW

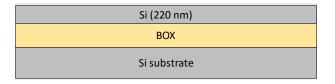

For this call, the patterns will be processed on a single-side polished Silicon-on-Insulator (SOI) wafer, with the following nominal parameters:

- Crystalline silicon (Si) substrate with the resistivity of 750  $\Omega$ .cm.

- Thermal silica (SiO<sub>2</sub>) Buried OXide (BOX) layer with a thickness  $h_{box} = 2 \mu m$

- Crystalline silicon (Si) core layer (100)-oriented with a thickness  $h_{wg}$  = 220 nm ± 20nm

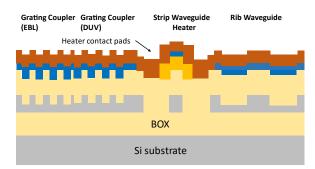

We will offer four silicon etch processes: 1) a shallow silicon etch of 94 nm  $\pm$  10 nm, 2) a shallow silicon etch of 70 nm  $\pm$  10 nm 3) an intermediate silicon etch of 120 nm  $\pm$  10 nm, and 4) a full silicon etch to the BOX layer. We will offer a 1  $\mu$ m  $\pm$  100 nm thick silicon dioxide top cladding layer with two metal layers for heaters: 1) heater filaments, and 2) heater contact pads.

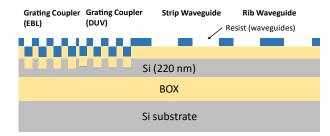

The schematic description of the process flow is given below:

1. Starting SOI substrate

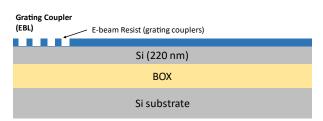

2. Resist patterning for Silicon Etch 1 (GDS layer 60) – 94 nm ± 10 nm etch

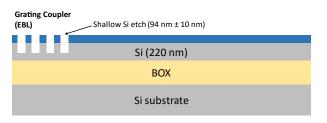

3. Shallow Si etch (94 nm ± 10 nm etch depth)

#### 4. Resist strip

| Grating Couple<br>(EBL) |              |  |

|-------------------------|--------------|--|

|                         | Si (220 nm)  |  |

|                         | BOX          |  |

|                         | Si substrate |  |

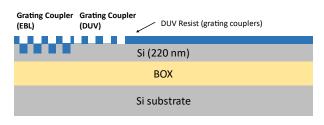

5. Resist patterning for Silicon Etch 2 (GDS layer 6) - 70 nm  $\pm$  10 nm etch

6. Shallow Si etch (70 nm ± 10 nm etch depth)

| Grating Coupler Grating Coup<br>(EBL) (DUV) | ler Shallow Si etch (70 nm ± 10 nm) |

|---------------------------------------------|-------------------------------------|

|                                             |                                     |

|                                             | Si (220 nm)                         |

|                                             | BOX                                 |

|                                             | Si substrate                        |

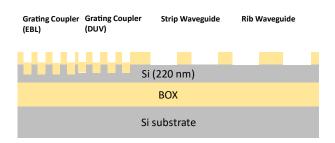

7. Resist strip

| Grating Coupler(<br>(EBL)    ( | Grating Coupler<br>(DUV) |

|--------------------------------|--------------------------|

|                                | Si (220 nm)              |

|                                | BOX                      |

|                                | Si substrate             |

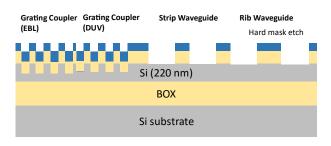

8. Silicon dioxide hard mask deposition – 250 nm

| Grating Coupler<br>(EBL) | Grating Coupler<br>(DUV)            |

|--------------------------|-------------------------------------|

|                          | SiO <sub>2</sub> hard mask (250 nm) |

|                          |                                     |

|                          | Si (220 nm)                         |

|                          | BOX                                 |

|                          | Si substrate                        |

9. Resist patterning for Silicon Etch 3 (GDS layers 3 & 4) – 120 nm ± 10 nm etch

10. Hard mask etch

11. Resist strip

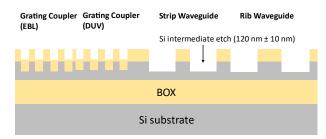

12. Intermediate Si etch (120 nm ± 10 nm etch depth)

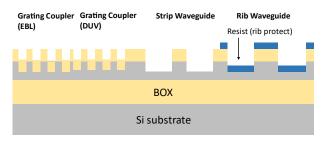

13. Resist patterning for Silicon Etch 4 (GDS layer 5) – 100 nm etch to BOX

#### 14. Si continuation etch to BOX (100 nm etch to BOX)

| Grating Coupler<br>(EBL) | Grating Coupler<br>(DUV) | Strip      | Waveguide   | Rib Waveg | guide |

|--------------------------|--------------------------|------------|-------------|-----------|-------|

| ()                       | ()                       | Si strip e | tch (100 nm | to BOX)   |       |

|                          |                          | ļ          |             | 6         |       |

|                          |                          | BOX        |             |           |       |

| Si substrate             |                          |            |             |           |       |

15. Resist strip

| Grating Coupler Grating Coupler<br>(EBL) (DUV) | Strip Waveguide | Rib Waveguide |

|------------------------------------------------|-----------------|---------------|

|                                                |                 |               |

|                                                | BOX             |               |

| Si                                             | substrate       |               |

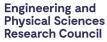

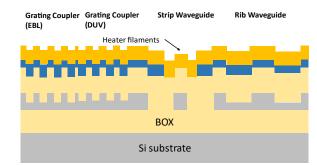

16. Deposition of 1  $\mu$ m ± 100 nm thick SiO2 top cladding

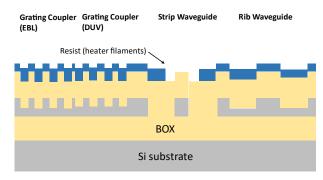

17. Resist patterning for Heater Filaments (GDS layer 39)

#### 18. Heater filament deposition

19. Metal lift-off

| Grating Coupler Grating Coupler<br>(EBL) (DUV) | Strip Waveguide | Rib Waveguide |

|------------------------------------------------|-----------------|---------------|

|                                                | . <b>1</b> 14   |               |

|                                                |                 |               |

|                                                | BOX             |               |

| S                                              | i substrate     |               |

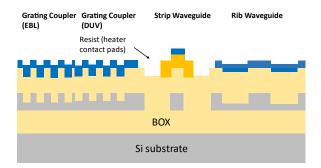

20. Resist patterning for Heater Contact Pads (GDS layer 41)

21. Heater contact pads deposition

#### 22. Metal lift-off

If you require any alternative processing steps (e.g. custom etch depths), we may be able to perform them for a small charge. Email <u>cornerstone@soton.ac.uk</u> with your request.

## 5. DESIGN RULES

It is important that designs conform to the following design rules to ensure clarity and correct processing.

## **5.1 DESIGN AREA**

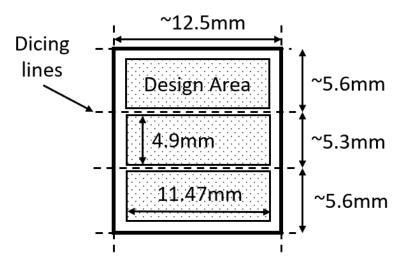

The standard user cell has dimensions of 11.47 x 4.9 mm<sup>2</sup> or 5.5 x 4.9 mm<sup>2</sup>.

#### **5.1.1 PHYSICAL DIE SIZE**

The physical size of the dies you will receive is approximately 12.5 x 5.3-5.6 mm<sup>2</sup>. This area includes a border the CORNERSTONE team will add that contains alignment marks, metrology boxes etc. which surround 3x design areas from various CORNERSTONE users, as shown in Figure 1. If you require specific physical die dimensions (12.5 x 5.3 mm<sup>2</sup> or 12.5 x 5.6 mm<sup>2</sup>), for example if integration to a PCB is required, please specify the physical die dimensions you require in the online mask submission form you are required to complete as part of the submission process (see Section 8)

#### **5.2 GDS LAYERS**

Each lithographic step in the fabrication process flow is identified by a specific GDS layer/s. These are as follows:

#### Silicon Etch 1 (Grating couplers/EBL)-GDS Layer 60(Dark field)-etch depth: 94 nm ±10 nm

This layer is used to define grating couplers, which are fabricated with 94 nm shallow silicon etching. Drawn objects on this layer will be patterned by Electron Beam lithography (EBL). The maximum exposure (drawing) area is limited to 55000  $\mu$ m<sup>2</sup>.

Silicon Etch 2 (Grating couplers/DUV)-GDS Layer 6(Dark field)-etch depth: 70 nm ±10 nm

This layer is used to define grating couplers, which are fabricated with 70 nm shallow silicon etching. Drawn objects on this layer will be patterned by deep-UV lithography.

<u>Silicon Etch 3 (Waveguide layer) – GDS Layer 3 (Light field) & GDS Layer 4 (Dark field) –</u> etch depth: 120 nm ± 10 nm

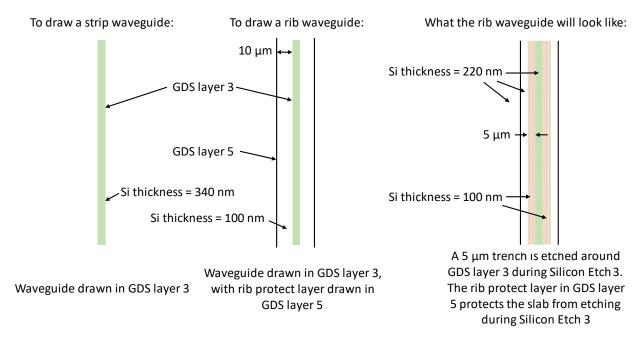

This layer defines both strip and rib waveguides (to form a rib waveguide, the slab region is protected during Silicon Etch 4 defined by GDS layer 5 – see below), and is split into two separate GDS layer numbers, patterned into the same resist and etched together:

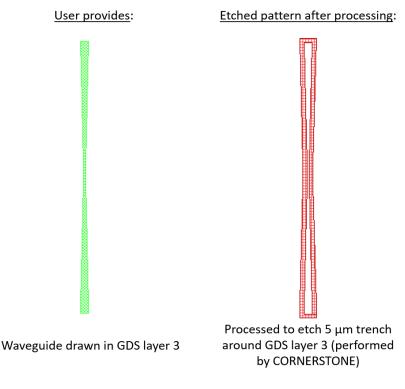

<u>GDS Layer 3</u>: Drawn objects on this layer will be protected from the silicon etch. Users should draw the waveguides and any other features to remain following 120 nm silicon etching (to the rib waveguide height). During fracturing processing, this will be translated into a pattern that defines 5 µm wide trenches on either side of the waveguides drawn in GDS layer 3 (see Figure 2).

If you require waveguide trenches that are a different width, refer to the guidelines for generating the trenches in Section 9. You can complete these steps yourself and modify the growth function dimension in step 1.

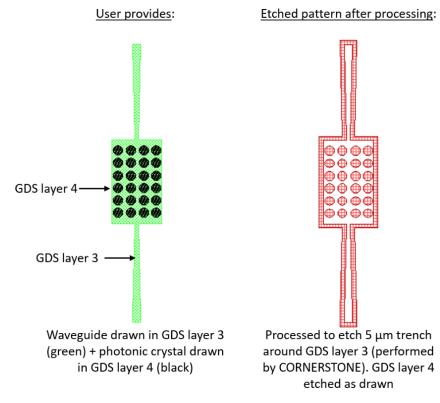

<u>GDS Layer 4</u>: Drawn objects on this layer will be exposed to the 120 nm silicon etch (to the rib waveguide height). An example photonic crystal structure is shown in Figure 3. The important thing to note here is that the waveguide layer drawn in GDS layer 3 should overlap the structures drawn in GDS layer 4, so that when the 5 µm trenches are generated by CORNERSTONE, a continuous waveguide remains.

#### <u>Silicon Etch 4 (Rib protect layer) – GDS Layer 5 (Light field) – etch depth: 100 nm to BOX</u>

This layer defines the protective layer for rib waveguides. Drawn objects in this layer will be protected from etching whilst the strip waveguides are etched to the BOX (all areas not previously defined in the Silicon Etch 3 layer will be protected from etching by a hard mask). We recommend that this layer should extend more than or equal to 5 µm from the edge of features drawn in GDS layer 3 so that the 5 µm wide trenches etched in the previous partial silicon etching step are fully protected by GDS layer 5, with the exception of any rib-to-strip transitions. An overview of how to draw both strip and rib waveguides is shown in Figure 4.

Figure 4 – Drawing strip and rib waveguides.

# Heater Filaments – GDS Layer 39 (Light field)

This layer defines the heater filaments. Drawn objects on this layer will remain after metal lift-off. It is recommended to use a filament width of 900 nm for the best compromise between heater power efficiency, phase tunability and robustness.

## Heater Contact Pads – GDS Layer 41 (Light field)

This layer defines the heater contact pads. Drawn objects on this layer will remain after metal lift-off.

An example heater layout for a straight waveguide is included in the .gdsll template file. The contact pads can be modified according to your probe design.

## <u>Cell Outline – GDS Layer 99</u>

This layer defines the design space boundaries (11.47 x 4.9 mm<sup>2</sup> or 5.5 x 4.9 mm<sup>2</sup>).

## <u> Labels – GDS Layer 100</u>

This layer defines text labels, which will be merged with Silicon Etch 3 (Waveguides) by the CORNERSTONE team. This layer will not have any design rule checking (DRC) performed.

Note: You do not need to add fabrication alignment marks to your design. Layer-to-layer alignment marks will be added by the CORNERSTONE team, placed outside the design area.

## 5.3 MINIMUM FEATURE SIZES, TARGET CRITICAL DIMENSIONS AND OTHER DESIGN RULES

- Minimum feature sizes, minimum gaps, and maximum feature widths for each GDS layer are detailed in Table 2.

- The target critical dimension for each GDS layer is listed in Table 2. Note that other feature sizes may have a small dimensional bias.

- A minimum spacing between waveguides of at least 5 µm is recommended to avoid power coupling.

- All structures drawn in GDS layer 6 & 60 (Grating couplers) must overlap by at least 200 nm with GDS layer 3 (Waveguides).

- An overlap of at least 10 µm between GDS layer 39 (Heater Filaments) and GDS layer

41 (Heater Contact Pads) is recommended for optimal heater performance.

- Ensure all structures drawn in GDS layer 6 (Grating couplers) do not overlap with either GDS layer 39 (Heater Filaments) or GDS 41 (Heater Contact Pads).

- Drawn area in GDS Layer 60 for the e-beam lithography is limited to 55000  $\mu m^2$ .

## 5.4 DESIGN RULES SUMMARY

A summary of the design rules and GDS layer numbers described in this section is detailed in Table 2 below.

| Layer description               | GDS<br>number | Field | Min.<br>feature<br>size | Min.<br>gap | Max.<br>feature<br>length |

|---------------------------------|---------------|-------|-------------------------|-------------|---------------------------|

| Silicon Etch 1 (94 nm ± 10 nm)  | 60*           | Dark  | 60 nm                   | 60 nm       | 20 µm                     |

| Silicon Etch 2 (70 nm ± 10 nm)  | 6             | Dark  | 200 nm                  | 250 nm      | 20 µm                     |

|                                 |               |       | 200 nm                  | 350 nm      | N/a                       |

| Silicon Etch 3 (120 nm ± 10 nm) | 3             | Light | 350 nm                  | 200 nm      | N/a                       |

|                                 | 4             | Dark  | 200 nm                  | 350 nm      |                           |

| Silicon Etch 4 (100 nm to BOX)  | 5             | Light | 250 nm                  | 250 nm      | N/a                       |

| Heater Filaments                | 39            | Light | 600 nm                  | 10 µm       | N/a                       |

| Heater Contact Pads             | 41            | Light | 2 µm                    | 10 µm       | N/a                       |

| Cell Outline                    | 99            | N/a   | N/a                     | N/a         | N/a                       |

| Labels**                        | 100           | Dark  | 250 nm                  | 250 nm      | N/a                       |

Table 2 – Design rules summary.

\*The total drawn area for electron beam lithography is limited (see section 5.3).

\*\*Features drawn in the Labels layer will be merged into Silicon Etch 3 by the CORNERSTONE team.

In order to help you ensure that you comply with the design rules, you can download and execute the KLayout pre-DRC script provided by CORNERSTONE on our website <u>www.cornerstone.sotonfab.co.uk/design-rules</u> (note that the automatic DRC will not check all of the design rules, so it remains very important to read the design rules in detail).

MPW users will have an opportunity to attend 1-to-1 Drop-in Session to pre-review mask layouts before the submission deadline, using the <u>link</u> to book a 20-mins session.

#### **5.5 FILE FORMAT**

Designs must be submitted in a Graphical Database System file (extension .gdsll) or Open Artwork System Interchange Standard (extension .oas) format. Ensure a manufacturing grid size of 1 nm is used, as per the CORNERSTONE GDSII Template file.

We recommend dedicated lithography editing software be used in the design of the .gdsll or .oas file.

#### 5.6 GDSII TEMPLATE FILE

A .gdsll template file has been made available on our website containing the information described in this section. Ensure that all submitted designs fit within the specified area, and that only the designated GDS layer numbers are used.

#### **6. MATERIAL PROPERTIES**

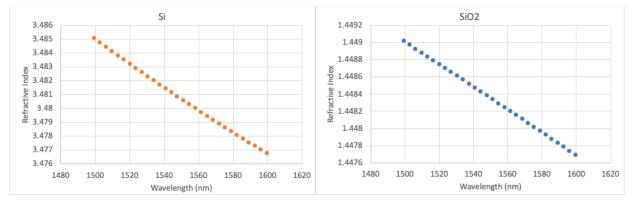

The measured refractive indices of Silicon and  $SiO_2$  layers are shown in Figure 5 below. This data is also available in tabular format on our website.

Figure 5 – Refractive indices of Silicon (left) and SiO<sub>2</sub> (right).

## 7. QUALITY ASSESSMENT

This fabrication run will be qualified by characterising a standard test pattern that is included on the chip (not part of the user cell). The test structures that will be checked after fabrication are reported in Table 3 below, together with the values that are targeted by the CORNERSTONE platform.

| Test structure                           | Parameter              | Value                 |

|------------------------------------------|------------------------|-----------------------|

| Straight single mode rib waveguide       | Propagation loss       | < 4 dB/cm for TE mode |

| Strip MZI integrated with the PDK heater | Phase shift efficiency | < 30 mW/π phase shift |

## 8. MASK SUBMISSION PROCEDURE

In order to be eligible to submit a design you must first sign-up to this call using the online form found using the link below. This is in order to enable us to prepare the necessary paperwork and plan the fabrication process effectively. The sign-up deadline is found at the top of this document.

#### www.cornerstone.sotonfab.co.uk/home/mpw-sign-up-form

Under no circumstances will we accept any design submissions for which we have not received a sign-up form.

After completing the sign-up form, when you are ready to submit your mask design on or before the mask submission deadline listed at the top of this document, follow the link below to the CORNERSTONE website mask submission page:

www.cornerstone.sotonfab.co.uk/gds-file-upload

A purchase order (PO) must be uploaded to this form to pay the access fee. Purchase orders will not be accepted via email.

You must also upload your design file to the submission form. Ensure that the top cell in your design file is titled 'Cell0\_[Name of Institution]'.

For information about setting up CORNERSTONE as a supplier to your institution, please contact <u>cornerstone@soton.ac.uk</u>.

## 9. MASK PROCESSING PERFORMED BY CORNERSTONE

Upon receipt of your design file, the CORNERSTONE team will perform the following mask processing steps in order to produce the final mask, based on the descriptions provided in Section 5.2:

<u>Silicon Etch 3 (Waveguide layer) – GDS Layer 3 (Light field) & GDS Layer 4 (Dark field) –</u> <u>etch depth: 120 nm ± 10 nm:</u>

- 1. Grow Waveguide layer (GDS layer 3) by 5 µm in all directions.

- 2. Subtract the Waveguide layer (GDS layer 3) from the output of (1) to produce the etch trenches around the drawn waveguides.

- 3. Merge the output of (2) with the dark field Waveguide Etch layer (GDS layer 4) and the Labels layer (GDS layer 100).

Silicon Etch 4 (Rib protect layer) – GDS Layer 5 (Light field) – etch depth: 100 nm to BOX:

1. Subtract the Rib Protect layer (GDS layer 5) from the Cell Outline (GDS layer 99) to convert to a dark field mask.

## **10. TECHNICAL SUPPORT**

If you have any questions relating to the fabrication process or design rules, please contact the CORNERSTONE team (<u>cornerstone@soton.ac.uk</u>).

# **11. DEVICE DELIVERY**

A total of 10 replica cells will be delivered to each user. The delivery time schedule can be found in Table 1.

# **12. FEEDBACK**

Feedback is essential to the CORNERSTONE team. It is required to ensure a continuous improvement to the quality of our services. It is also evidence on the user satisfaction, and a measure to what extent we were able to meet user requirements. Therefore, we kindly ask our users to provide feedback to us, including device performance data, SEM images, future interests for the CORNERSTONE project etc. A feedback form will be sent to you along with your chips.

Alternatively, email <u>cornerstone@soton.ac.uk</u> with your comments.

# **13. PUBLICATIONS**

If you are benefitting from subsidised access via the C-PIC funding, please include the following statement in the "Funding" section of any publications:

"The chip fabrication for this research was funded by the Engineering and Physical Sciences Research Council (EPSRC) C-PIC (EP/Z531066/1) project."

This is important to us to be able to demonstrate impact from the funding.

If you are a paying user, we kindly ask that you include CORNERSTONE in the "Acknowledgments" section of any publications that result from the chips you receive from CORNERSTONE.